PCIExpress 构架 如图 2 所示,即 PCI Express |0">PCIExpress 的层次体系结构。它保持了与 PCI寻址模式(加载-存储体系结构且具有单层地址空间)的兼容性,从而保证了所有现有的应用程序和驱动操作无需改变。PCI Express 配置使用的是PCI 即插即用标准中所定义的标准机制。软件层发出读和写请求,并使用基于数据包、分段传输的协议通过处理层传输至I/O 设备。 链路层向这些数据包添加序列号和循环冗余校验(CRC )从而创建了一个高度可靠的数据传输机制。基本的物理层包括两个单工通道,即传输对和接收对。这个传输对和接收对一起被称为一个信道。2.5 Gb/s 的初始速度提供了在每个PCI Express 信道上每个方向上大约250 MB/s 标准带宽。一旦考虑协议头,这其中大约200 MB/s 由设备用来传输数据。这一速率是大多数典型 PCI 设备的 2 番到 4 番。而且不同于 PCI 的是,只要总线带宽在设备之间共享,每一个设备都 具有此带宽。 物理层 基本的PCI Express 链路包括两个低电压的AC 耦合差分信号对(一个传输对和一个接收对),如图3所示。物理链路层信号使用一个去加重(de-emphasis )策略来减少符号间干扰,从而提高了数据完整性。数据时钟通过使用 8b/10b 的解码策略来嵌入,从而到达极高的数据传输率。初始的信号发生频率是每个方向 2.5 Gb/s (生成1个信号) 而且它将会随着硅工艺的提高而增加至每个方向10 Gb/s(信号在铜线中传输可能实现的最大速率)。两个链路层的 PCI Express 代理在物理层上传输数据包。图3 PCI Express 物理连接图一个PCI Express 链路层的带宽可能通过增加信号对形成多个信道而线性增长。物理层提供 x1, x2, x4, x8, x12, x16 和x32 信道宽度,理论上它将输入的数据包在这些信道上分配。使用 8b/10b 编码方式,每一个字节在这些信道上传输。数据的分拆和整合对于其他层来说是透明的。在初始化阶段,每个PCI Express 链路通过链路两端代理的信道宽度的匹配和频率操作来建立。在这其中没有固件和操作系统软件的参与。PCI Express 体系结构提供了将来通过速度升级和高级编码技术所带来的性能提升。将来的速度、编码技术或者媒介仅仅会影响物理层。 在PCI Express 中使用不同的信道宽度需要用户注意扩展板要求的带宽以及与母板提供的带宽相匹配。除了图形卡以外(通常是X16 ),许多早期的PCI Express 扩展板使用的 X1 的宽度。随着更高的带宽要求,越来越多的板卡将使用更宽的带宽。早期的PCI Express 计算机提供一个X16 的连接器以及一些X1 、X4 、X8 插槽的组合,这由计算机面向的客户所决定。PCI Express 允许在不匹配的信道宽度上进行一些交互操作,这取决于不匹配的方向。在一个较小宽度的连接器上使用更大宽度的扩展板卡是向下插入。例如,利用PCI ,您可以在一个32 位的插槽上插入一个64 位的PCI 板卡。 然而,在 PCI Express 中,向下插入在物理上被扩展板卡和连接器所阻止。另一中不匹配在一个较大的连接器上使用一个较小的扩展板卡是向上插入。向上插入是允许的,但是会受到限制在这种配置下,母板厂商需要支持仅在X1 数据率上的扩展板卡,从而浪费了在具有更快接口速率的扩展板卡上的投资。无论一个特定的母板在向上插入配置时能否在全速率时处理一个扩展板卡,都必须在每种情况下向母板生产商确认。例如,一些母板可以在一个X4 的扩展板卡插入一个X8 或X1 的插槽时,以全速率(X4 )进行处理,然而来自同一厂商的其他母板可能仅以X1 的速率运行。在一个母板既带有集成图形控制器(板载)又带有一个 X16 的 PCI Express 插槽以用于将来图形扩展的情况下,通常不可能在板载图形卡使能的同时使用那个 X16 的插槽。 数据链路层 链路层的主要作用就是保证数据包在 PCI Express 链路上的可靠传输。链路层负责数据完整性并向处理层的数据包添加序列号和循环冗余校验,如图4所示。大部分数据包在处理层初始化。一个基于优先数的、流量控制的协议保证了数据包仅在另一端具有接收这个数据包的缓冲区情况下才能传输,这样就去除了任何数据包的请求以及由于资源限制而引起的总线带宽浪费。链路层会自动的重新收发一个被标记为损坏的数据包。 处理层 处理层接收软件层的读和写请求,并创建请求数据包发送至链路层。所有的请求都被分段的处理而且一些请求包需要一个响应包。处理层也从链路层接收响应数据包并且将它与原先的软件请求相匹配。每一个数据包都具有一个唯一的标识,使得响应包能够指向正确的源。数据包的格式提供了32 位的存储地址和扩展的64 位地址。数据包也具有诸如“无侦听”、“灵活排序”“优先级”等属性,这可能用于将这些数据包在I/O 子系统中以最优的路径传输。 处理层提供4 个地址空间3 个PCI 地址空间(内存、I/O 和配置)和消息空间。PCI 2.2 引入了另一种广播系统中断的方式称为消息信号中断(MSI )。作为PCI 2.2 系统中一种可选的性能, 这里使用了一种特殊格式的内存写处理替代硬连接的边带信号。PCI Express 技术指标重新使用了MSI 概念以作为一种主要的中断处理方式,并且使用了消息空间来接收所有的优先的边带信号来作为带内信号,例如中断、电源管理请求,和复位。其它PCI 2.2 技术指标中的“特殊周期”,例如中断确认,也被处理成带内消息。您可以将 PCI Express 消息视为“虚拟的线”,因为他们的作用是消除当前平台上所使用的各种边带信号。 软件层 软件兼容性对于 PCI Express 是极为重要的。软件兼容性有两个方面初始化(或者列举)和运行时刻。PCI 具有一个功能强大的初始化模式,其中操作系统可以发现所有当前添加的硬件设备然后分配系统资源,例如内存、I/O 空间和中断,从而创建一个优化的系统环境。PCI 配置空间和I/O 设备可编程能力是PCI Express 体系结构中保持不变的重要概念。PCI 所使用的运行时刻软件模式是一个加载-存储、共享内存的模式,它在PCI Express 体系结构中得以保持以使得所有现有的软件能够无需改变即可执行。新的软件也可以利用一些PCI Express 最新的先进特性,例如高级开关(本文并未述及)。

推荐内容

-

什么是PCI Express 标准(中)

-

同步器作用

-

无功功率真的没用吗?

-

测量误差如何界定?

-

宁波“数字菜篮子”紧急上线来货预约二维码

-

厦门开展预售资金监管进账智能管理 保障购房人合法权益

-

宁波市鄞州区利用大数据战“疫”,为疫情防控配上“最强大脑”

-

接来电1.3万多个!宁波市镇海区矛调中心全力保障12345热线畅通

-

“浙里办”推出掌上救助申请,不用请社区(村)代办

-

全国首创的“方舱保”,为医护人员及工作人员提供全方位风险保障

-

调动资本参与养老金融服务 满足养老保险消费者多样化需求

-

170余名“行政点长”化身“疫情防控一线督导员”

-

宁波两家方舱医院52名患者出院

-

最新!宁波市鄞州区、海曙区、江北区、高新区调整“三区”范围

-

对不起它们

-

一季度中国GDP同比增长4.8%

-

随迁老人承受身心双重压力的同时还面临“福利鸿沟”——补齐权益缺失 让“老漂族”心有所归

-

一季度中国经济开局总体平稳

-

数字盘点:中国空间站 扎实迈好每一步

-

涉案40万元!渝中警方破获一起假冒日化品销售案

-

知网回应被中科院停用:不属实

-

绿绿绿~这满目翠色的北碚,你爱了吗?

-

河南省“十四五”现代物流业发展规划出炉

-

新城控股62.32亿元小公募债券项目状态更新为“已反馈”

-

太平鸟在经营上显露疲态 抄袭和质量问题严重

-

让民生福祉更有“质感”

-

镇海建设品质之城,打造幸福美好家园

-

LINE FRIENDS成立中国泛娱乐事业部,全面推进数字化战略转型

-

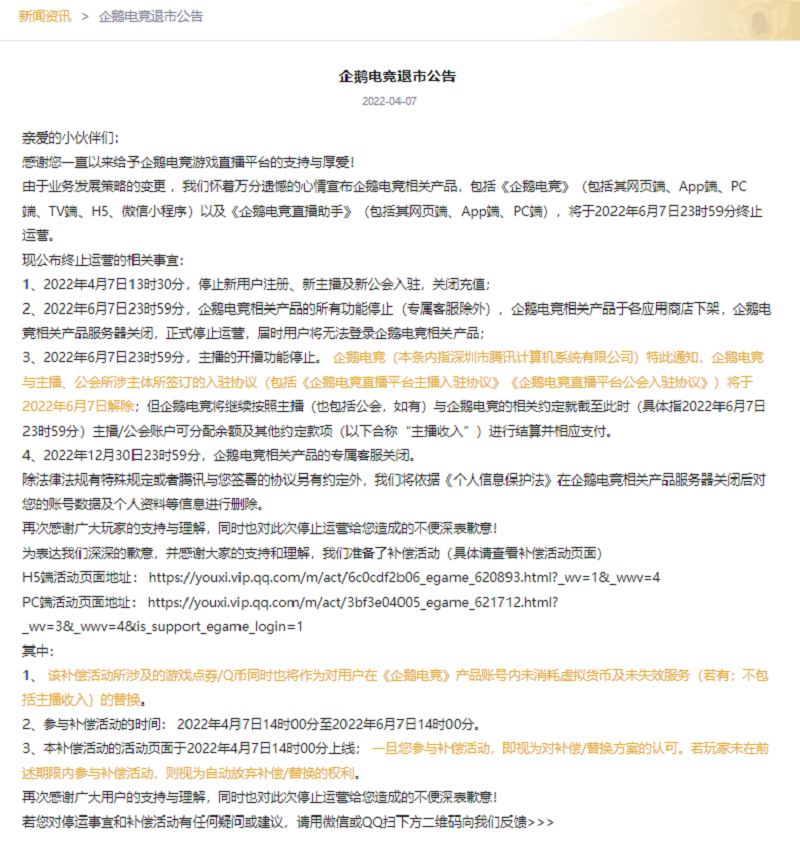

企鹅电竞即将谢幕 未来游戏直播行业还有发展空间吗?

-

20余名村民跳着彝族达体舞,以村内最高礼仪迎接宁波宁海

-

上海建工2021年营收增加21.5% 毛利率创五年新低

-

机构:市场信心修复仍需时间 预计全国商品房销售规模同比降幅仍维持高位

-

时隔两年,负油价事件内幕曝光!12名交易员合谋,单日收割7亿美元

-

被自己人坑了!瑞幸bug订单挤爆门店,有人“1分钱喝了两杯”

-

退市倒计时,拉夏贝尔A股“梦碎”

-

宁波4件作品入围第十五届中国民间文艺山花奖

-

诠释宋式美学,尽显鄞州风雅!宁波两位画家作品在中国美术馆亮相

-

广汽讴歌退出成为必然 外来豪华品牌找不准中国消费者喜好

-

“搬”进农家书屋,“上”了城乡公交专线

-

喜讯!4件宁波作品获第十五届中国民间文艺山花奖

-

五部门联合开展2022年度宁波市“新时代好少年”活动

-

宁波正式入汛排水管网开展全面“体检”

-

宁波市急救中心全面建成11分钟急救圈

-

京杭运河二通道320国道桥轮廓初显4月底完成

-

贵州不断健全县域金融组织体系 加大对小微企业的支持力度

-

微光成炬,守护大家——育芽团志愿者在行动

-

杭州市临平区获省平安建设最高荣誉“一星平安金鼎”

-

疫情防控不能松懈!杭州市临区卫健局立案查处36家医疗机构

-

沈阳和平区快速推动复工复产 实施重点行业专班化管理

-

疫情无情人有情!杭州临平区崇贤街道辖区企业为“三区”提供三千份便当

-

杭州亚运会临平赛区首场亚运测试赛开赛

-

沈阳开展“征信修复”乱象治理“百日行动” 促进征信业健康发展

-

杭州临平山公园300余种杜鹃花明艳绽放吸引市民观赏

-

辽宁朝阳169个重点项目集中开工 涵盖高质量工业项目等四大类

-

多家银行提供多方位金融服务 对接广交会参会客商的金融需求

-

广州税务建立“一企一策”税收服务团队服务助力广交会

-

山大“你好,未来!”职业生涯教育微课堂正式开启

-

过敏自救指南|100个中国人里约有40个会过敏

-

济南起步区绘就现代版“鹊华秋色图”

-

济南小伙为千余名癌症患者做假发 每顶背后都有故事

-

山大心理中心举办“在禅绕画中静心当下”活动

-

山东济南历下公安分局龙洞派出所开展普法宣传活动

-

农行山东分行助力小微企业和个体工商户抗疫纾困

-

国家统计局:一季度GDP同比增长4.8%

-

马蹄有什么作用与功效

-

黏玉米和水果玉米区别

-

水果玉米和正常玉米的区别

-

科普不能太“离谱”,警惕披着科普外衣的“段子”

-

水果玉米和普通玉米怎么区分

-

欧美多国报告不明病因儿童肝炎病例◇300049 福瑞股份

-

胸腔里引流出“牛奶”,咋回事?

-

嘴唇变厚、鼻子变大、手和脚也莫名增大,可能不仅仅是因为长胖了

-

智慧大脑 健康你我|宝宝平躺吃夜奶,长大颜值受影响

-

过敏、炎症等免疫系统疾病日趋高发,全国首个2型炎症皮肤病规范化诊治协作网建立

-

江苏医疗队创新管理助沪抗疫

-

许昆林主持召开省疫情联防联控指挥部会议 突出重点区域领域 防止疫情反弹反复——许昆林主持召开省疫情联防联控指挥部会议

-

蜂蜜治疗萎缩性鼻炎怎么做?

-

广德市新杭市场监管所四举措扎实推进餐饮单位疫情防控工作

-

12345民声在线|4月19日上午十点宿迁市医疗保障局走进直播室!

-

上海国资经营拟4月25日对“18沪国01”付息,利率4.9%

-

华润股份:完成发行20亿元中期票据 票面利率3.3%

-

超洗脑!泰国旅游中文宣传曲《萨瓦迪卡曼谷》来袭,听完带你秒回天使之城!

-

UST市值超越BUSD,成为市值第三的稳定币

-

上海浦西首批团长14天开21个团:手把手教老人买菜 不后悔为爱发电

-

银行股普跌!招商银行一度跌超8%,回应称正在核查原因

-

继阿联酋之后,大龙网数字贸易帮助安徽本地企业再拓欧洲市场

-

平安守护者行动 守护你的金融权益——平安普惠宿州分公司联合西关派出所开展维C行动

-

陕西发改委:部分煤矿受国家限价影响消极生产,导致中长期合同履约率较低

-

马蹄怎么做好吃最简单

-

武汉市第三医院12名医护人员组成援沪医疗队

-

疫情下的鄄城县人民医院血透室 温暖有爱有担当

-

濮阳一批集中带量采购医用耗材20日起降价

-

如皋:做好防控近视工作 切实保护学生视力健康

-

江西通报10批次食品不合格 涉及农兽药残留等问题

-

健康专家号丨血脂指标因人而异,高危人群更应严格控制

-

市中心医院聚焦学科建设服务高质量发展

-

上海第一医药开启“基本保障+特殊用药”需求登记服务

-

长春:近三日新增感染者数较前期明显下降,疫情整体形势向好

-

【警界先锋】痴迷破案的“熊猫警长”倒下了

-

在吗?小哥哥

-

株洲诗人陈招生组诗四首:赞美人间四月天 感恩当下幸福泉

-

银桦路社区开展“垃圾分好类”主题垃圾分类二维码宣传活动

-

重庆体育人 | 巴南冯成文:重拾运动七年,每天坚持健走30000步

-

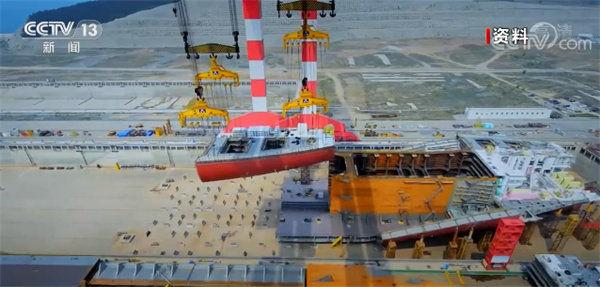

国内双线铁路箱梁架设最小曲线半径刷新纪录

-

渝北区双凤桥街道:防骗宣传面对面,守住群众“钱袋子”

-

我国成功发射大气环境监测卫星

-

车牌损坏?请一定及时重办!

-

为疫情防控仪器设备体检,让诊疗设备精准有效

-

专家呼吁:API遭攻击事件增多 安全能力亟待提升

-

神秘的“00”来电,不要接!

-

市场流动性充裕 央行公开市场今日实现零投放零回笼

-

IDC:中国市场领涨全球,浪潮全闪存储连续3个季度稳居中国前二

-

10余省份完成提前下达额度发行工作 专项债券拉动有效投资

-

创造更多“从0到1”原创成果——从科技奖励看广东创新走向

-

IBIS建模——第1部分:为何IBIS建模对设计成功至关重要

-

长沙先导控股将对“21先导02”债券付息 票面利率为4.50%

-

中信证券:4月或5月的LPR利率有一定可能会跟随调整

-

三台载荷随大气环境监测卫星成功入轨,进一步提升我国大气环境监测能力

-

申赎变动|东方可转债债券开放100万元以上大额申购

-

数件商品价格无依据 聚美优品被罚1万元

-

燃油价格飙升下 英国民众对制裁俄罗斯支持意愿正下降

-

大丰农商行成A股首家IPO被否银行:发审委要求说明部分集团客户贷款余额超过授信总额原因

-

美好医疗首发获通过:对境外单一客户重大依赖 上市委要求说明是否对持续经营构成重大不利影响

-

双杯生椰拿铁只要4元?瑞幸致歉:价格错误,已紧急取消订单

-

捷途大圣的国潮,是怎么玩的?

-

成都自贸区市场主体发展迅猛 创新因子不断被激活

-

多地一季度投资完成率实现“开门红” 重点领域项目加快推进

-

安徽酒店业推出“套餐”和“摆摊”销售形式 进一步开拓销量增长

-

“浙水好喝”数字化平台已100%覆盖城乡居民 满足居民用水需求

-

安徽已培育形成21个百亿级集群 创新能力持续增强

-

上海市科技创业中心多措并举助企纾困 做细做实政策服务

-

智梭无人车跑步入场 无接触配送迫在眉睫

-

手指变粗竟是肺癌前兆?出现这些症状,疾病可能正悄悄靠近…

-

第一位接受青霉素临床治疗的病人,究竟因为什么死亡?

-

"维生素D"又被表扬了!研究表明:它是免疫力的神助攻

-

恒温杯垫不插电可以用吗

-

身体这个部位过度敏感,到底有多痛苦?

-

今日新闻精选

-

预防静脉血栓 保障生命健康 市人民医院开展“无栓病房”建设

-

崆峒区市场监管局召开医疗器械质量安全风险隐患排查整治工作安排部署会议

-

邯郸市慢特病“掌上办”申报认定达3.7万人

-

赌博上瘾 不可忽视的精神障碍

-

一发现就是中晚期?其实它一直在疯狂暗示

-

调味有机更健康 食光往事为你打造饮食新菜单

-

体育培训火了,训练成果如何?桂花网用蓝牙技术明明白白告诉你

-

大连金普新区开展民营企业“法治体检”活动 优化法治化营商环境

-

踏春出行,哪款SUV是更适合的伙伴?

-

大连海参品牌最新排名大洗牌!!辽连湾海参突出重围!!

-

嘉兴经开区启动“无疫工地”创建活动 107个项目已复工复产

-

量大不等于力强!海信新风空调打造清新空气标杆

-

烟台自贸片区聚焦“企业开办”等三大指标 再造“一体两翼”

-

公安部网安局:这些涉疫骗局要注意!

-

13人盗墓被抓,数百页“盗墓笔记”曝光!

-

获取淡水资源有新招 超强仿生蜘蛛丝规模化高效集水

-

这个警察哥哥好暖!

-

5G新通话不简单:不仅听见,还能看懂

-

山西清徐农商银行:“三举措”金融助力共战疫

-

我的警号和爸爸一样

-

安庆构建可持续发展的绿色交通 新能源公交车比例将提升至75%以上

-

安庆网约车新规征求社会意见 近期确定车辆最终具体标准

-

纳米限域金属离子/质子双向快速整流传输机制揭示

-

关于1名援建省外方舱医院返回人员核酸检测阳性情况的通报

-

离成都不远,不仅是个古镇,还有着伊斯兰风味!

-

闻喜农商银行多项措施助力疫情防控

-

安庆市去年全市累计收购粮食80.4万吨 今年力争粮油加工总产值190亿元以上

-

我国成功发射中星6D星

-

不同手型如何选手链?

-

邮储银行张家口市分行全面推广“EMS小微企业寄递卡”

-

全市安全生产大检查启动 坚决遏制各类生产安全事故发生

-

绝不屈服命运的不公,为女儿治病母亲求助轻松筹获积极响应

-

第131届广交会“云”开幕,线上平台基础架构全面更新

-

毒贩驾车逃跑,民警死死抓住车门追击,手掌被夹骨折……

-

六安市公布五起涉疫违法典型案例

-

早间公告:中环海陆向不特定对象发行可转债申请获受理

-

一季度安庆“最紧俏”职业公布 汽车生产线操作工、缝纫工、织布工、焊工、铸造工排名前五

-

邮储银行张家口市分行践行普惠金融

-

“白鹭”警察周建华,棒棒哒!

-

欧洲央行官员Muller:资产购买计划刺激措施可能在7月结束

-

湖北十堰市兑现3300万元水环境质量横向生态奖补金

-

农发行郧阳区支行荣获“金融支持经济高质量发展优秀单位”称号

-

俄媒:乌克兰要求G7提供500亿美元财政援助,并考虑发行零息债券

-

天房发展8.88亿元私募债券获上交所受理

-

工信部推动在沪工业企业复工复产 保障重点产业链运转顺畅

-

椰树延续“土味”招聘广告风格 “四有”承诺背后带有诸多附加条款

-

一季度全国房地产开发投资27765亿元,同比增长0.7%

-

联影医疗科创板IPO首发过会:上市委要求说明营业收入大幅增长是否可持续

-

1—3月份全国固定资产投资(不含农户)增长9.3%

-

3月份规模以上工业增加值增长5.0%,产品销售率下降2个百分点

-

一季度生产原煤10.8亿吨,同比增长10.3%,进口煤炭下降24.2%

-

接种疫苗对防止重症效果显著

-

厘清边界种真“草”

-

乳腺癌患病人群越来越年轻化 患者往往有“四高”的情况

-

糖尿病血糖升高不可怕 常生活中该如何控制血糖?

-

鼻咽癌患者要注意 治疗结束后需注意这些问题

-

慢淋发病率呈逐年上升趋势 “长期规范治疗”的推进难度加大

-

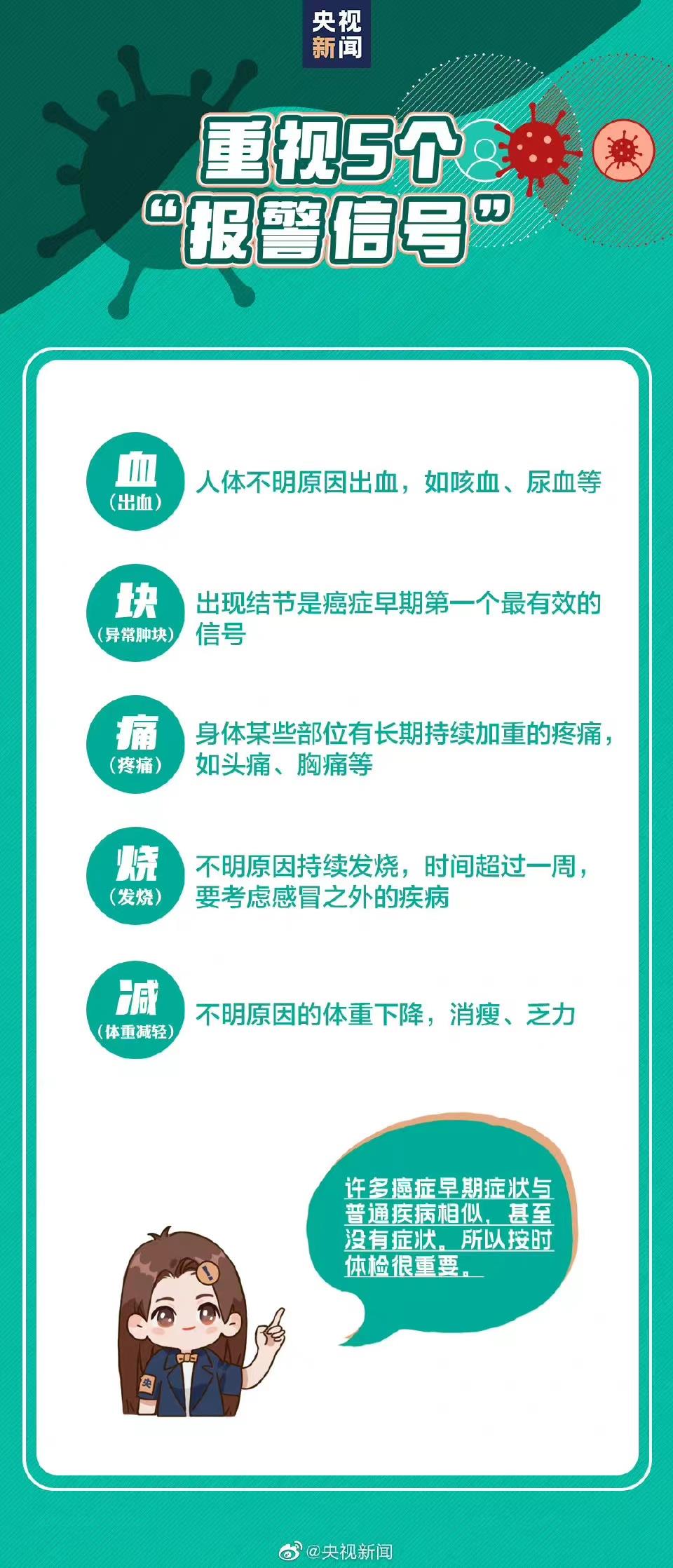

肿瘤和癌症是一回事吗?癌症的危险信号都有哪些?

-

春季孩子身高的生长速度较高 如何抓住长高黄金时间?

-

不少年轻人开启减肥计划 如何减少碳水化合物的摄入?

-

全国手足口病呈隔年高发的特点 预防应从这几点入手

-

调味有机更健康 食光往事为你打造饮食新菜单