保证覆盖率的同时优化仿真回归

随着应用要求的激增和用户需求的增加,硬件设计变得更加复杂。市场趋势的快速变化,以及对电动汽车等技术的更多关注,决定了对高效电源管理和高性能处理的需求水涨船高。随着 SoC 设计规模的扩大,复杂程度的增加,验证吞吐量仍然是一个瓶颈,单纯依靠增加 CPU 核数量和运行更多的并行测试治标不治本。上述因素的叠加让验证工程师面对复杂设计的压力与日俱增。

(资料图片)

(资料图片)

验证永远不会完成;当你的时间用完时,它就结束了。目标是在你耗尽时间之前使验证过程收敛。每个人都希望看到关键指标收敛到目标,并在严格的成本和时间限制下做到这一点。想象一下,坐在驾驶舱里,向黑匣子输入信息,然后等待奇迹发生(按一个按钮,你的工作就完成了)。当务之急是人工智能和机器学习(AI/ML)如何帮助我们更快地完成回归,节省调试时间,实现验证/覆盖率目标,并管理资源和资金——换句话说,我们如何使用 AI/ML 来提高验证的效率?

瑞萨公司也面临着类似的挑战。市场压力和严格的投片时间表促使他们寻找一种技术/方法来优化仿真回归,并在整个产品开发过程中加速设计验证过程。他们希望减少风险,尽早发现尽可能多的错误,能够快速调试,并满足其终端用户的要求。

瑞萨开始探索 Cadence Xcelium 机器学习应用。这个应用程序使用机器学习技术来优化仿真回归,以产生一个更紧凑的压缩回归。然后这个优化的回归被用来重现与原始回归几乎相同的覆盖率,并通过运行现有随机测试平台可能出现的边界场景,快速找到设计错误。

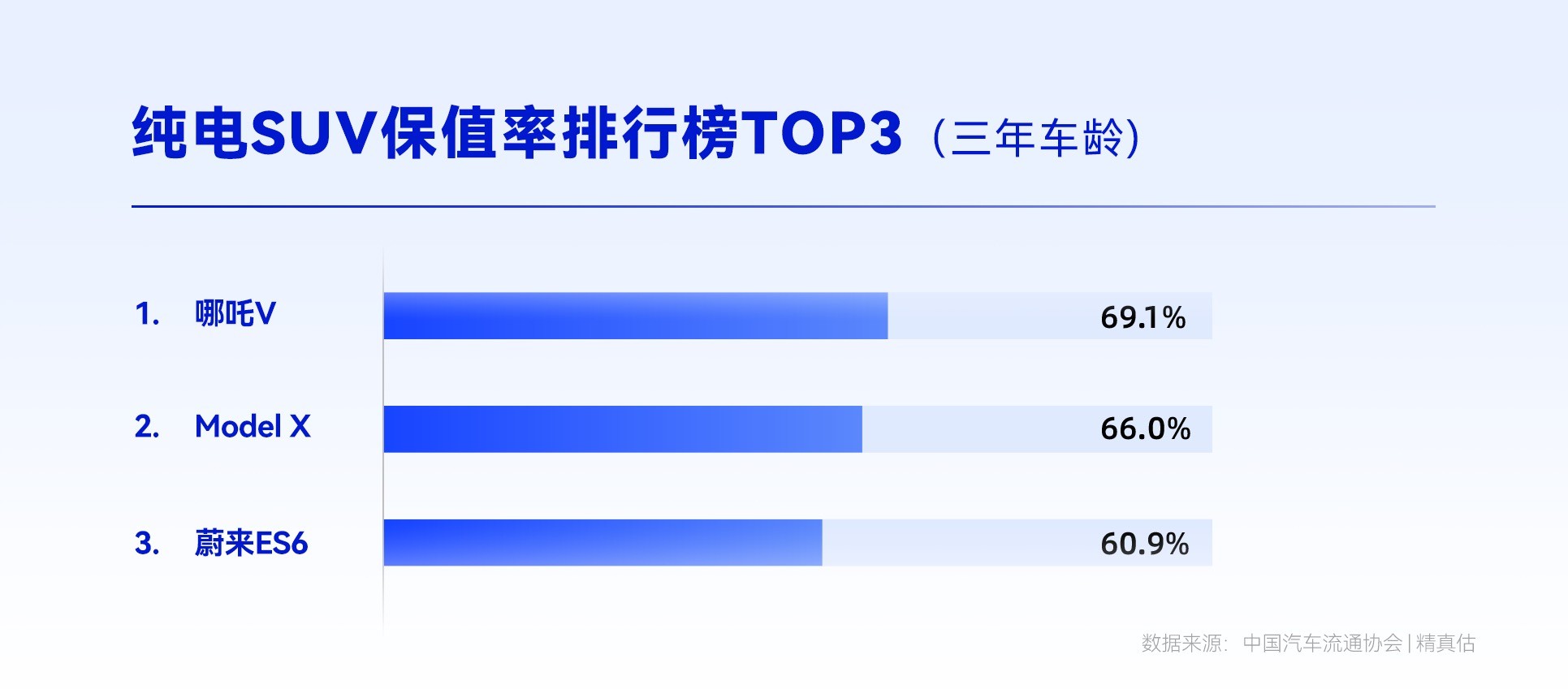

瑞萨的测试结果非常完美,整个随机验证回归的时间缩短了 66%,大幅节省了资源,成本和时间。Xcelium ML App 帮助瑞萨在保证 100%覆盖率的同时将压缩效率提高 2.2 倍。此外,将 ML 回归用于首次设计迭代时,瑞萨再次实现了 100%覆盖率下,将时间缩短 3.6 倍。

基于 ML 的测试回归次数仅为 1168,相当于 3774 次原始回归的 1/3。实现目标所需时间缩短了 30%,满足了严格的上市需求。

除了利用 Xcelium ML App 节省资源和时间,加速实现设计收敛,瑞萨也评估了由 3款 Verisium App 组成,基于 AI 的 Cadence Verisium 平台,将验证生产力提高了 6 倍,共节省 27 个工时。

瑞萨评估的App 如下:

Verisium AutoTriage,一款基于 ML 的自动化测试失败分类程序,可以将相同错误导致的测试失败自动分组。失败分组耗时降低了 70%,整体效率提升了 3.3 倍。

Verisium SemanticDiff 帮助瑞萨快速识别失败原因,比传统 diff 工具更加高效。SemanticDiff 专注于设计环境,可以提供更相关的差异分析。此外,逐条检查 diff 指令的历史文件是很繁琐的,SemanticDiff app 可以大幅缩短纠错时间,显著提升效率。

Verisium WaveMiner 可以高效识别差异点,用户可以在 PASS 和 FAIL 中将差异点可视化,便捷地比较 PASS 和 FAIL 的波型及源代码。瑞萨的纠错时间得以缩短 89%-97%,带来 9 倍的效率提升。

Cadence 的 Verisium 平台和 Xcelium ML 应用一起提供了一套利用 AI/ML 的应用,以优化验证工作负载,提高覆盖率,并加速复杂 SoC 上设计错误的根源分析。瑞萨公司利用人工智能平台,将其验证生产率提高了 10 倍。

关于Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续九年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站www.cadence.com。