FPGA Conference Europe 是欧洲领先的可编程逻辑器件专家会议。在越来越受人工智能驱动的云数据中心、电信和许多其他高性能应用中,现场可编程门阵列(简称 FPGA)早已证明自己是适用于各种任务的灵活且强大的加速器解决方案。

2022年欧洲 FPGA 大会,于 7 月 5 日至 7 日在德国慕尼黑东会议中心举办,3天100%专业知识!75个来自全球顶级专家演讲。讨论嵌入式系统的开发人员必须处理新的解决方案和方法,但同时也要澄清基本问题:FPGA 是否适合他们自己的项目?使用 FPGA 的最佳方式是什么?瑞苏盈科作为参展商出席了此次会议并发表演讲!

【资料图】

【资料图】

欧洲FPGA大会现场

来自Enclustra的演讲者:

Speaker from Enclustra:

(高级FPGA/SoC逻辑软件工程师)。Harry Commin于2013年在伦敦帝国学院获得电子工程博士学位,并在FPGA和ASIC设计和实现方面工作了9年。他的主要兴趣是在数字信号处理和(无线)数字通信系统领域。

演讲摘要:

高效的基于FPGA的DSP,速度高达GS/s

随着带宽要求的不断提高,数字信号处理(DSP)技术必须不断发展以支持越来越高的采样率。当采样率超过时钟频率时,就需要并行的DSP技术,而现成的解决方案变得很难找到。

同时,并行DSP并不是每个问题的最佳解决方案。如果采样率小于或等于时钟频率,那么传统的DSP实现就更有效率。因此,为一项任务设计的DSP可能不适合在不同的采样率下执行完全相同的功能。这使得高效的DSP设计成为一项复杂且可能耗时的任务。

在这次演讲中,我们展示了我们如何应对这些挑战。介绍了我们的通用DSP库,它可以最大限度地减少低采样率的开发时间(直到时钟频率)。然后,重点介绍了广泛使用的并行DSP模块的设计、实现和分析,如FIR滤波器、重采样和FFT,能够处理许多GS/s。

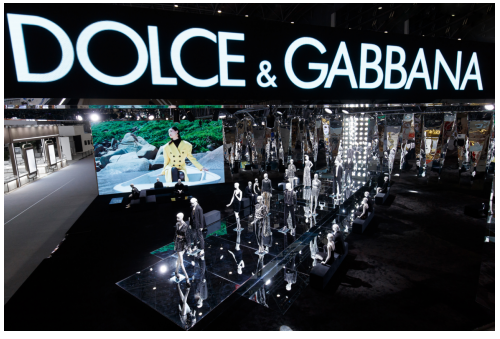

瑞苏盈科展台现场

除了展示我们最新和高度集成的系统级模块的展位外,Harry Commin 还展示了如何简化和加快基于 FPGA 的数字信号处理系统的开发。过去用 FPGA 实现数字信号处理很困难,因为它必须用 VHDL 或 Verilog 来描述。这就是 Enclustra为 FPGA 设计开发 DSP 库的原因。«Efficient FPGA-Based DSP up to GS/s» 演示文稿展示了如何在很短的时间内以图形方式组装整个数字信号处理系统。该库包括 FIR 和 CIC 滤波器、CORDIC、函数逼近、缓冲器和时分复用基础设施,并支持连续波和脉冲处理。

为了进一步简化和加速开发,DSP 库还包含基于开源 Python 框架的位真仿真模型。这允许使用 Python 的全部功能和易用性来测试、模拟和优化确切的功能。

今天我们把欧洲最前沿的 FPGA 大会内容免费分享给大家,如果想获取演讲PPT,请扫描二维码下载查看。

想要了解更多Enclustra Universal DSP Library IP Solution 信息,请访问:

https://www.enclustra.com/en/products/ip-cores/universal-dsp-library/

本文及演讲文档为原创内容,版权归「瑞苏盈科」所有。转载请注明出处,谢谢。

![[房屋鉴定 都市检测] 都市检测荣获“科技型中小企业”](http://www.meijiezaixian.net/ueditor/php/upload/image/20220727/1658887522242672.png)